互联网技术对人类社会的影响不言而喻。当今大部分电子设备都能以不同的方式接入互联网(Internet),在家庭中PC常见的互联网接入方式是使用路由器(Router)组建小型局域网(LAN),利用互联网专线或者调制调解器(modem)经过电话线网络,连接到互联网服务提供商(ISP),由互联网服务提供商把用户的局域网接入互联网。而企业或学校的局域网规模较大,常使用交换机组成局域网,经过路由以不同的方式接入到互联网中。

The impact of Internet technology on human society is self-evident. Most electronic devices today have access to the Internet (Internet) & #xff0c in different ways; the means of Internet access common to PCs in households are the use of routers (Router) to organize small local area networks (LAN) & #xff0c; the use of Internet special lines or modems (modem) to access telephone lines & #xff0c; connections to Internet service providers (ISP) & #xff0c; access to the Internet by Internet service providers.

39.1 互联网模型

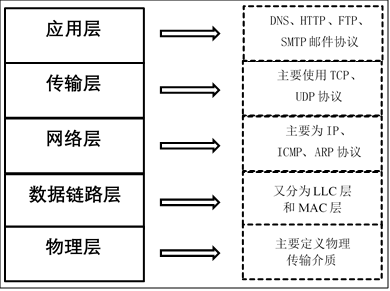

通信至少是两个设备的事,需要相互兼容的硬件和软件支持,我们称之为通信协议。以太网通信在结构比较复杂,国际标准组织将整个以太网通信结构制定了OSI模型,总共分层七个层,分别为应用层、表示层、会话层、传输层、网络层、数据链路层以及物理层,每个层功能不同,通信中各司其职,整个模型包括硬件和软件定义。OSI模型是理想分层,一般的网络系统只是涉及其中几层。

Communications are at least two devices xff0c; there is a need for compatible hardware and software support xff0c; what we call communication protocols xff0c. Tethernet communications are more complex in structure xff0c; ISO has developed the OSI model xff0c for the entire Tethernet communication structure; total seven layers xff0c; application layers, expression layers, session layers, transmission layers, network layers, data chain layers and physical layers xff0c; different layers xff0c; functional #xff0c for divisions in communications xff0c; the entire model includes hardware and software definitions. The OSI model is the ideal layer xff0c; general network systems cover only a few of these layers.

TCP/IP是互联网最基本的协议,是互联网通信使用的网络协议,由网络层的IP协议和传输层的TCP协议组成。TCP/IP只有四个分层,分别为应用层、传输层、网络层以及网络访问层。虽然TCP/IP分层少了,但与OSI模型是不冲突的,它把OSI模型一些层次整合一起的,本质上可以实现相同功能。

TCP/IP is the most basic protocol for the Internet & #xff0c; the network protocol for Internet communications & #xff0c; it consists of the IP protocol for the network layer and the TCP protocol for the transmission layer. TCP/IP has only four layers & #xff0c for the application layer, the transmission layer, the network layer and the network access layer, respectively. Although the TCP/IP layer is less xff0c; it is not conflicted with the OSI model xff0c; it integrates some layers of the OSI model xff0c; it is essentially capable of achieving the same function.

实际上,还有一个TCP/IP混合模型,分为五个层,参考图?391,它实际与TCP/IP四层模型是相通的,只是把网络访问层拆成数据链路层和物理层。这种分层方法对我们学习理解更容易。

In fact xff0c; there is also a TCP/IP hybrid model xff0c; it is divided into five layers xff0c; reference map?391xff0c; it is actually connected to TCP/IP four-layer model xff0c; it is simply a network access layer that is broken down into data links and physical layers. This stratification is easier for us to learn to understand.

图?391 TCP/IP混合参考模型

Figure? 391 TCP/IP hybrid reference model

设计网络时,为了降低网络设计的复杂性,对组成网络的硬件、软件进行封装、分层,这些分层即构成了网络体系模型。在两个设备相同层之间的对话、通信约定,构成了层级协议。设备中使用的所有协议加起来统称协议栈。在这个网络模型中,每一层完成不同的任务,都提供接口供上一层访问。而在每层的内部,可以使用不同的方式来实现接口,因而内部的改变不会影响其它层。

When designing the network xff0c; to reduce the complexity of the network design xff0c; to encapsulate the hardware, software, xff0c; these layers form a network system model. Dialogue between the two devices on the same floors, communication engagements xff0c; form a hierarchy agreement. All protocols used in the device are collectively referred to as the protocol pads. In this network model xff0c; each layer performs different tasks xff0c; interfaces are provided for access to the upper layer. At each level xff0c; interfaces xff0c; they can be achieved in different ways; thus internal changes do not affect the other layers.

在TCP/IP混合参考模型中,数据链路层又被分为LLC层(逻辑链路层)和MAC层(媒体介质访问层)。目前,对于普通的接入网络终端的设备,?LLC层和MAC层是软、硬件的分界线。如PC的网卡主要负责实现参考模型中的MAC子层和物理层,在PC的软件系统中则有一套庞大程序实现了LLC层及以上的所有网络层次的协议。

In the TCP/IP hybrid reference model xff0c; the data chain layer is again divided into LLC layers (logical chain layers) and MAC layers (media medium access layers). xff0c; currently xff0c; for general access network terminals xff0c;? LLC and MAC layers are soft and hardware dividing lines. For example, the PC netcard is primarily responsible for achieving the MAC sub-layer and physical layer of the reference model xff0c; and in the PC software system there is a large set of procedures to achieve all network-level agreements at the LLC level and above.

由硬件实现的物理层和MAC子层在不同的网络形式有很大的区别,如以太网和Wi-Fi,这是由物理传输方式决定的。但由软件实现的其它网络层次通常不会有太大区别,在PC上也许能实现完整的功能,一般支持所有协议,而在嵌入式领域则按需要进行裁剪。

The physical and MAC sublayers realized by hardware are very different in different forms of the network xff0c; for example, by the Tainet and Wi-Fi, this is determined by physical transmission. But other network levels realized by the software usually do not differ much xff0c; full functionality xff0c may be achieved on the PC; all protocols xff0c are generally supported; and in embedded areas, tailoring is required.

39.2 以太网

以太网(Ethernet)是互联网技术的一种,由于它是在组网技术中占的比例最高,很多人直接把以太网理解为互联网。

The Ethernet is a type of Internet technology xff0c; as it accounts for the highest share of cluster network technology xff0c; many directly interpret it as the Internet.

以太网是指遵守IEEE 802.3标准组成的局域网,由IEEE 802.3标准规定的主要是位于参考模型的物理层(PHY)和数据链路层中的介质访问控制子层(MAC)。在家庭、企业和学校所组建的PC局域网形式一般也是以太网,其标志是使用水晶头网线来连接(当然还有其它形式)。IEEE还有其它局域网标准,如IEEE 802.11是无线局域网,俗称Wi-Fi。IEEE 802.15是个人域网,即蓝牙技术,其中的802.15.4标准则是ZigBee技术。

Ethernet refers to the local area network (LAN) of compliance with the IEEE 802.3 standard & #xff0c; the medium access control sublayer (MAC) as defined by the IEEE 802.3 standard, mainly located in the physical layer of the reference model (PHY) and in the data chain layer. The PC local area network (LAN) of households, enterprises and schools is also generally organized in the form of the Tainet & #xff0c; it is marked by the use of the crystal head network (and, of course, other forms). IEE has other local area network (LAN) standards xff0c; IEE 802.11 is the wireless area network xff0c; popularly known as Wi-Fi. IEE 802.15 is the personal area network xff0c; i.e., bluetooth technology ff0c; of which the criterion 802.15.4 is ZigBee technology.

现阶段,工业控制、环境监测、智能家居的嵌入式设备产生了接入互联网的需求,利用以太网技术,嵌入式设备可以非常容易地接入到现有的计算机网络中。

At this stage xff0c; industrial controls, environmental monitoring, smart home embedded equipment generate demand for Internet access xff0c; use of Ethernet technology xff0c; embedded equipment can be accessed very easily into existing computer networks.

39.2.1?PHY层

在物理层,由IEEE 802.3标准规定了以太网使用的传输介质、传输速度、数据编码方式和冲突检测机制,物理层一般是通过一个PHY芯片实现其功能的。

In the physical layer & #xff0c; transmission media, transmission speed, data coding and conflict detection mechanisms used in the Tainet are specified by the IEEE 802.3 standard & #xff0c; the physical layer is generally functional through a PHY chip.

1.传输介质

传输介质包括同轴电缆、双绞线(水晶头网线是一种双绞线)、光纤。根据不同的传输速度和距离要求,基于这三类介质的信号线又衍生出很多不同的种类。最常用的是"五类线"适用于100BASE-T和10BASE-T的网络,它们的网络速率分别为100Mbps和10Mbps。

Transfer media include coax cable, double strangulation (the crystalhead net line is a double strangulation line), fibre optics. Signal lines based on these three types of media generate many different types according to different transmission speed and distance requirements xff0c. The most commonly used are 34; five types 34; networks xff0c for 100 BASE-T and 10BASE-T; their network rates are 100 Mbps and 10 Mbps, respectively.

2.编码

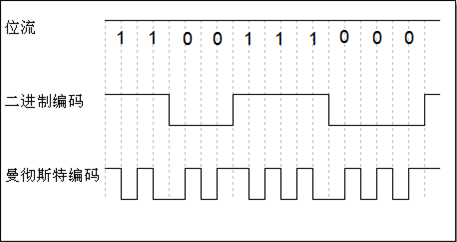

为了让接收方在没有外部时钟参考的情况也能确定每一位的起始、结束和中间位置,在传输信号时不直接采用二进制编码。在10BASE-T的传输方式中采用曼彻斯特编码,在100BASE-T中则采用4B/5B编码。

In order to allow recipients to determine each starting, ending and intermediate position without external clock reference xff0c; do not directly use binary code when transmitting signals. Manchester code xff0c is used in 10 BASE-T transmission; and 4B/5B code is used in 100 BASE-T.

曼彻斯特编码把每一个二进制位的周期分为两个间隔,在表示"1"时,以前半个周期为高电平,后半个周期为低电平。表示"0"时则相反,见图?392

Manchester code divides each binary cycle into two intervals xff0c; in 34; 134; xff0c; in the previous half-cycle high xff0c; in the second half low. 34; 034; in the opposite case xff0c; see figure 392.

图?392?曼彻斯特编码

Figure? 392 Manchester code.

采用曼彻斯特码在每个位周期都有电压变化,便于同步。但这样的编码方式效率太低,只有50%。

The Manchester code has voltage changes xff0c in each bit cycle; it is easy to synchronize. But it is too inefficient to encode xff0c; only 50%.

在100BASE-T?采用的4B/5B编码是把待发送数据位流的每4位分为一组,以特定的5位编码来表示,这些特定的5位编码能使数据流有足够多的跳变,达到同步的目的,而且效率也从曼彻斯特编码的50%提高到了80%。

The 4B/5B code used in 100BASE-T is a group of xff0c for each four-digit stream of data to be sent; xff0c for a specific five-digit code; xff0c for a sufficient number of jumps in data streams; xff0c for synchronizing purposes; and the efficiency has increased from 50 per cent to 80 per cent of Manchester code.

3.CSMA/CD冲突检测

早期的以太网大多是多个节点连接到同一条网络总线上(总线型网络),存在信道竞争问题,因而每个连接到以太网上的节点都必须具备冲突检测功能。以太网具备CSMA/CD冲突检测机制,如果多个节点同时利用同一条总线发送数据,则会产生冲突,总线上的节点可通过接收到的信号与原始发送的信号的比较检测是否存在冲突,若存在冲突则停止发送数据,随机等待一段时间再重传。

Early Ethernets are mostly multiple nodes connected to the same network bus (the bus type network) & #xff0c; there is a question of competition between the believers & #xff0c; therefore each node connected to Ether must have a conflict detection function. Ethernet has CSMA/CD conflict detection mechanisms & #xff0c; if multiple nodes simultaneously use the same bus to send data xff0c; there is a conflict xff0c; nodes on the bus can detect conflict xff0c; if there is a conflict, stop sending data xff0c; wait randomly for retransmission.

现在大多数局域网组建的时候很少采用总线型网络,大多是一个设备接入到一个独立的路由或交换机接口,组成星型网络,不会产生冲突。但为了兼容,新出的产品还是带有冲突检测机制。

Most LANs are now organized with little bus network xff0c; most are connected to an independent route or switch interface xff0c; make up a star network xff0c; there is no conflict. But for compatibility xff0c; new products are still conflict detection mechanisms.

39.2.2?MAC子层

1.MAC的功能

MAC子层是属于数据链路层的下半部分,它主要负责与物理层进行数据交接,如是否可以发送数据,发送的数据是否正确,对数据流进行控制等。它自动对来自上层的数据包加上一些控制信号,交给物理层。接收方得到正常数据时,自动去除MAC控制信号,把该数据包交给上层。

The MAC sublayer is the lower part of the data chain layer xff0c; it is primarily responsible for data interfaces with the physical layer xff0c; e.g., is it possible to send data xff0c; is the correct data sent xff0c; controls the data flow etc. It automatically adds some control signals to the data package from the upper layer xff0c; is given to the physical layer. The recipient receives the normal data xff0c; automatically removes the MAC control signal xff0c; and hands the data package over to the upper layer.

2.MAC数据包

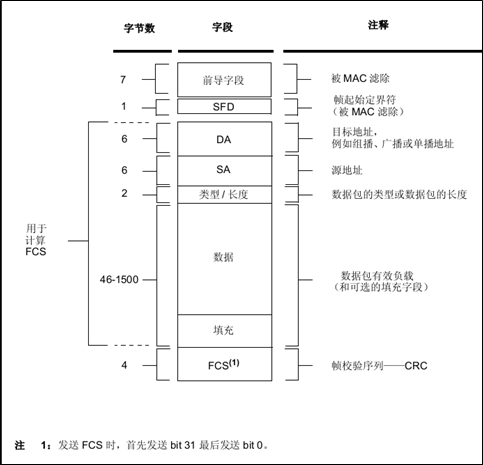

IEEE对以太网上传输的数据包格式也进行了统一规定,见图?393。该数据包被称为MAC数据包。

IEEE also has harmonized provisions on the format of the data package transmitted on the Tai Web xff0c; see figure 393. The data package is known as the MAC data package.

图?393 MAC数据包格式

Figure? 393 MAC data package format

MAC数据包由前导字段、帧起始定界符、目标地址、源地址、数据包类型、数据域、填充域、校验和域组成。

The MAC data package consists of a prefix field, frame start boundary, target address, source address, data package type, data field, fill field, check and domain.

?前导字段,也称报头,这是一段方波,用于使收发节点的时钟同步。内容为连续7个字节的0x55。字段和帧起始定界符在MAC收到数据包后会自动过滤掉。

? The lead field & #xff0c; also the header & #xff0c; this is a wave & #xff0c; it is used to synchronise the clocks of the sent and received nodes. 0x55 with seven consecutive bytes. The field and frame start boundary are automatically filtered when the MAC receives the data package.

?帧起始定界符(SFD):用于区分前导段与数据段的,内容为0xD5。

? Frame start delimiter (SFD) & #xff1a; xff0c for distinguishing the lead from the data segment; content 0xD5.

?MAC地址: MAC地址由48位数字组成,它是网卡的物理地址,在以太网传输的最底层,就是根据MAC地址来收发数据的。部分MAC地址用于广播和多播,在同一个网络里不能有两个相同的MAC地址。PC的网卡在出厂时已经设置好了MAC地址,但也可以通过一些软件来进行修改,在嵌入式的以太网控制器中可由程序进行配置。数据包中的DA是目标地址,SA是源地址。

The MAC address xff1a; the MAC address consists of 48 digits xff0c; it is the physical address of the web card xff0c; it is the bottom xff0c; it is the data received and received from the MAC address. Some of the MAC addresses are used for broadcasting and overlaying xff0c; there are no identical MAC addresses in the same network. The PC's web card was set up at the time of the factory xff0c; it can also be modified by some software xff0c; it can be configured by program in embedded #xff0c controllers. The DA in the data package is the target address xff0c; SA is the source address.

?数据包类型:本区域可以用来描述本MAC数据包是属于TCP/IP协议层的IP包、ARP包还是SNMP包,也可以用来描述本MAC数据包数据段的长度。如果该值被设置大于0x0600,不用于长度描述,而是用于类型描述功能,表示与以太网帧相关的MAC客户端协议的种类。

?Sat type xff1a; this region can be used to describe this MAC data package as an IP package belonging to the TCP/IP layer, ARP package or SNMP package & #xff0c; it can also be used to describe the length of the data segment of this MAC data package. If the value is set to be greater than 0x0600xff0c; not for length & #xff0c; but for type characterization function xff0c; and to indicate the type of MAC client protocol associated with the ultranet.

?数据段:数据段是MAC包的核心内容,它包含的数据来自MAC的上层。其长度可以从0~1500字节间变化。

? data segment & #xff1a; data segment is the core content of the MAC package & #xff0c; it contains data from the upper layers of the MAC. Its length can vary from 0 to 1500 bytes.

?填充域:由于协议要求整个MAC数据包的长度至少为64字节(接收到的数据包如果少于64字节会被认为发生冲突,数据包被自动丢弃),当数据段的字节少于46字节时,在填充域会自动填上无效数据,以使数据包符合长度要求。

?fill fields & #xff1a; because the protocol requires a minimum length of 64 bytes for the entire MAC data package (the data package received is considered to conflict if it is less than 64 bytes & #xff0c; the data package is automatically discarded) & #xff0c; when the bytes of the data field are less than 46 bytes & #xff0c; invalid data xff0c are automatically filled in the fill field; so that the data package meets the length requirements.

?校验和域:MAC数据包的尾部是校验和域,它保存了CRC校验序列,用于检错。

? Verify domain & #xff1a; the end of the MAC data package is the check & field & #xff0c; it saves the CRC verification sequence & #xff0c; used for error check.

以上是标准的MAC数据包,IEEE 802.3同时还规定了扩展的MAC数据包,它是在标准的MAC数据包的SA和数据包类型之间添加4个字节的QTag前缀字段,用于获取标志的MAC帧。前2个字节固定为0x8100,用于识别QTag前缀的存在;后两个字节内容分别为3个位的用户优先级、1个位的标准格式指示符(CFI)和一个12位的VLAN标识符。

These are the standard MAC data package & #xff0c; IEE 802.3 also provides for an extended MAC data package & #xff0c; QTag prefix field & #xff0c, which adds four bytes between the standard MAC data package's SA and the data package type; MAC frame, which is used to obtain the logo. The first two bytes are fixed at 0x8100, #xff1b, which is used to identify the existence of the prefix of QTag; the second two bytes are the three-bit user priority, one-bit standard format indicator (CFI) and one 12-digit VLAN identifier.

39.3 TCP/IP协议栈

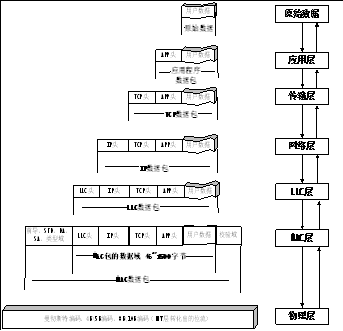

标准TCP/IP协议是用于计算机通信的一组协议,通常称为TCP/IP协议栈,通俗讲就是符合以太网通信要求的代码集合,一般要求它可以实现图?391中每个层对应的协议,比如应用层的HTTP、FTP、DNS、SMTP协议,传输层的TCP、UDP协议、网络层的IP、ICMP协议等等。关于TCP/IP协议详细内容推荐阅读《TCP-IP详解》和《用TCP/IP进行网际互连》理解。

The standard TCP/IP agreement is a set of protocols used for computer communications & #xff0c; commonly known as TCP/IP Protocol Lodge & #xff0c; popularly referred to as the code set meeting Ethernet communication requirements & #xff0c; generally required to make it possible to achieve the map? The corresponding protocols in each of the 391 layers & #xff0c; such as the application layers HTTP, FTP, DNS, SMTP & #xff0c; transmission layers tCP, UDP, IP on the network layer, ICMP, etc. The details of the TCP/IP protocol are recommended for reading the TCP-IP Detail and TCP/IP Interconnectivity Understanding.

Windows操作系统、UNIX类操作系统都有自己的一套方法来实现TCP/IP通信协议,它们都提供非常完整的TCP/IP协议。对于一般的嵌入式设备,受制于硬件条件没办法支持使用在Window或UNIX类操作系统的运行的TCP/IP协议栈,一般只能使用简化版本的TCP/IP协议栈,目前开源的适合嵌入式的有uIP、TinyTCP、uC/TCP-IP、LwIP等等。其中LwIP是目前在嵌入式网络领域被讨论和使用广泛的协议栈。本章内容其中一个目的就是移植LwIP到开发板上运行。

Windows operating systems, UNIX operating systems have their own set of methods to achieve TCP/IP communications protocols & #xff0c; they all provide a very complete TCP/IP protocol. For generic embedded equipment & #xff0c; subject to hardware conditions, there is no way to support the use of TCP/IP stores operating in Windows or UNIX operating systems & #xff0c; a simplified version of TCP/IP protocol & #xff0c is generally available; the current source is suitable for embedded uIPs, TinyTCPs, uC/TCP-IPs, LwIPs, etc. LwIPs are currently discussed and used in embedded network areas. One of the purposes of this chapter is to transplant LwIP to the development board.

39.3.1?为什么需要协议栈

物理层主要定义物理介质性质,MAC子层负责与物理层进行数据交接,这两部分是与硬件紧密联系的,就嵌入式控制芯片来说,很多都内部集成了MAC控制器,完成MAC子层功能,所以依靠这部分功能是可以实现两个设备数据交换,而时间传输的数据就是MAC数据包,发送端封装好数据包,接收端则解封数据包得到可用数据,这样的一个模型与使用USART控制器实现数据传输是非常类似的。但如果将以太网运用在如此基础的功能上,完全是大材小用,因为以太网具有传输速度快、可传输距离远、支持星型拓扑设备连接等等强大功能。功能强大的东西一般都会用高级的应用,这也是设计者的初衷。

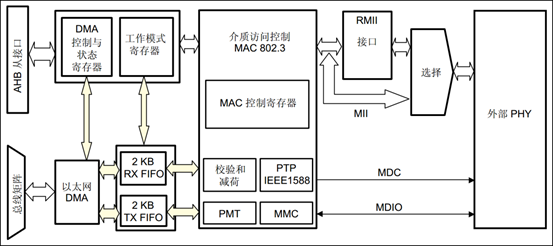

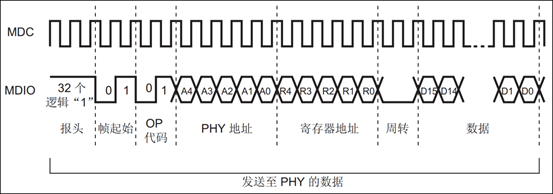

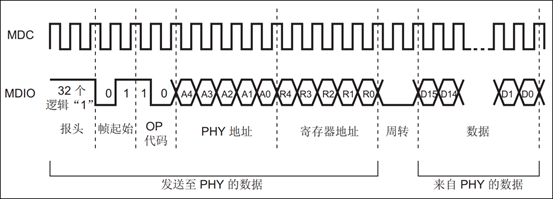

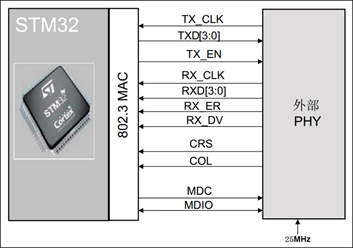

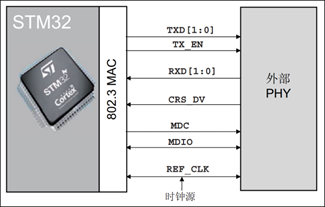

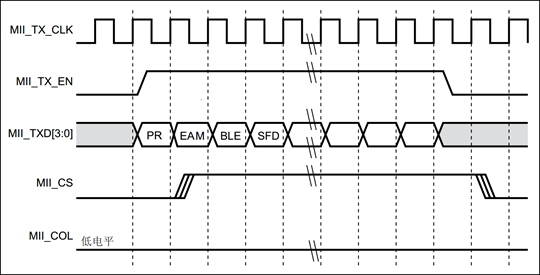

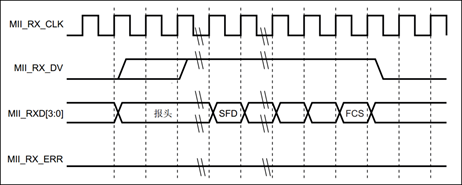

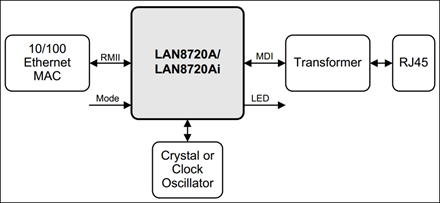

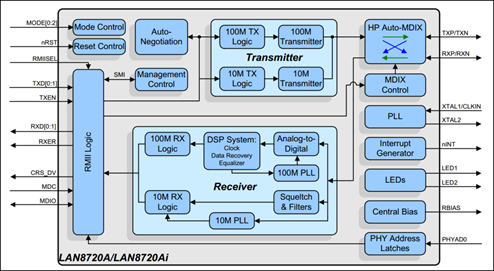

The physical layer of 使用以太网接口的目的就是为了方便与其它设备互联,如果所有设备都约定使用一种互联方式,在软件上加一些层次来封装,这样不同系统、不同的设备通讯就变得相对容易了。而且只要新加入的设备也使用同一种方式,就可以直接与之前存在于网络上的其它设备通讯。这就是为什么产生了在MAC之上的其它层次的网络协议及为什么要使用协议栈的原因。又由于在各种协议栈中TCP/IP协议栈得到了最广泛使用,所有接入互联网的设备都遵守TCP/IP协议。所以,想方便地与其它设备互联通信,需要提供对TCP/IP协议的支持。 xff0c is used to facilitate interconnection with other devices; if all equipment is agreed to use an interconnection mode xff0c; if some layers are added to the software to encrypt xff0c; so that it becomes relatively easy to communicate with different systems and different equipment. And as long as the new equipment is also used in the same way xff0c; can communicate directly with other equipment previously present on the network. That is why a network agreement at other levels above MAC and why it is used. Also because xff0c is the most widely used in the TCP/IP stacks of agreements; so xff0c; want to easily communicate with other equipment xff0c; and need to provide support for TCP/IP agreements. 用以太网和Wi-Fi作例子,它们的MAC子层和物理层有较大的区别,但在MAC之上的LLC层、网络层、传输层和应用层的协议,是基本上同的,这几层协议由软件实现,并对各层进行封装。根据TCP/IP协议,各层的要实现的功能如下: For example xff0c for Tainet and Wi-Fi; for their MAC sub-layers and physical layers xff0c; for the LLC layer, network layer, transmission layer and application layer above MAC xff0c; for the xff0c, which is essentially the same xff0c; for the software to achieve xff0c; and for the packaging of layers. According to TCP/IP protocols xff0c; for the functions to be performed by the layers xff1a; LLC层:处理传输错误;调节数据流,协调收发数据双方速度,防止发送方发送得太快而接收方丢失数据。主要使用数据链路协议。 LLC layer & #xff1a; processing transmission error & #xff1b; reconciling data streams & #xff0c; coordinating the speed of sending and receiving data & #xff0c; preventing the sender from sending data too fast for the recipient to lose the data. 网络层:本层也被称为IP层。LLC层负责把数据从线的一端传输到另一端,但很多时候不同的设备位于不同的网络中(并不是简单的网线的两头)。此时就需要网络层来解决子网路由拓扑问题、路径选择问题。在这一层主要有IP协议、ICMP协议。 The network layer xff1a; this layer is also known as the IP layer. The LLC level is responsible for transferring data from one end of the line to the other xff0c; however, many times different devices are located in different networks (not two headlines of a simple network line). The network level is required at this point to resolve subnetular problems, path selection. There are mainly IP protocols and ICMP protocols at this level. 传输层:由网络层处理好了网络传输的路径问题后,端到端的路径就建立起来了。传输层就负责处理端到端的通讯。在这一层中主要有TCP、UDP协议 Transfer layer & #xff1a; & #xff0c; end-to-end path created after network level has been processed. Transfer layer handles end-to-end communication. There are mainly TCP and UDP protocols in this layer. 应用层:经过前面三层的处理,通讯完全建立。应用层可以通过调用传输层的接口来编写特定的应用程序。而TCP/IP协议一般也会包含一些简单的应用程序如Telnet远程登录、FTP文件传输、SMTP邮件传输协议。 The application layer & #xff1a; the first three levels of processing & #xff0c; the communication is fully established. The application layer can be used to create specific applications by calling interfaces in the transfer layer. The TCP/IP protocol typically also contains simple applications such as Telenet remote login, FTP file transfer, SMTP mail transfer protocol. 实际上,在发送数据时,经过网络协议栈的每一层,都会给来自上层的数据添加上一个数据包的头,再传递给下一层。在接收方收到数据时,一层层地把所在层的数据包的头去掉,向上层递交数据,参考图?394。 In fact xff0c; xff0c at the time the data are sent; xff0c at every level xff0c at the network protocol store; the data from the upper level is added to the head of the previous data package xff0c; it is transmitted to the next level. xff0c at the time the data is received; the head of the layer is removed from the top layer xff0c; the data is transmitted to the upper level xff0c; reference chart?394. 图?394?数据经过每一层的封装和还原 Figure 394? The data are sealed and restored at each level. STM32F42x系列控制器内部集成了一个以太网外设,它实际是一个通过DMA控制器进行介质访问控制(MAC),它的功能就是实现MAC层的任务。借助以太网外设,STM32F42x控制器可以通过ETH外设按照IEEE 802.3-2002标准发送和接收MAC数据包。ETH内部自带专用的DMA控制器用于MAC,ETH支持两个工业标准接口介质独立接口(MII)和简化介质独立接口(RMII)用于与外部PHY芯片连接。MII和RMII接口用于MAC数据包传输,ETH还集成了站管理接口(SMI)接口专门用于与外部PHY通信,用于访问PHY芯片寄存器。 The STM32F42x series controller has an internal collection of xff0c, which is a media access control (MAC),, implemented via a DMA controller. Its function is to achieve the MAC layer. The xff0c, STM32F42x controller is capable of sending and receiving the MAC data package according to IEEE 802.3-2002 standards via ETH external. The ETH own DMA controller is used for MAC& #xff0c; ETH supports two industry standard interface interfaces independent interfaces (MII) and simplified media independent interfaces (RMII) for connection with external PHY chips. MII and RMII interfaces are used for MAC data package transmission xff0c; ETH interfaces are also dedicated to station management interfaces (SMI) with external PHY communications #xff0c; and access to PHY chips. 物理层定义了以太网使用的传输介质、传输速度、数据编码方式和冲突检测机制,PHY芯片是物理层功能实现的实体,生活中常用水晶头网线+水晶头插座+PHY组合构成了物理层。 The physical layer defines the transmission medium, transmission speed, data coding and conflict detection mechanisms used in Tainet & #xff0c; the PHYs is the entity that achieves the functions of the physical layer & #xff0c; the life crystalline & #43; crystal plug #43; and the PHY combination forms the physical layer. ETH有专用的DMA控制器,它通过AHB主从接口与内核和存储器相连,AHB主接口用于控制数据传输,而AHB从接口用于访问"控制与状态寄存器"(CSR)空间。在进行数据发送是,先将数据有存储器以DMA传输到发送TX FIFO进行缓冲,然后由MAC内核发送;接收数据时,RX FIFO先接收以太网数据帧,再由DMA传输至存储器。ETH系统功能框图见图?395。 ETH has a dedicated DMA controller & #xff0c; it connects the interface with the kernel and memory via AHB master & #xff0c; the AHB main interface is used to control data transmission & #xff0c; while AHB is used from the interface to access 34; the control and state repository & #34; CSR space. The data are sent xff0c; the data are transferred to DMA to send TX FIFO for buffer #xff0c; then xff1b is sent by MAC internal nuclems; xff0c; RX FIFO receives data first from the hypernet data frame #xff0c; and then by DMA to the repository. 图?395 ETH功能框图 Figure? 395 ETH function frames SMI是MAC内核访问PHY寄存器标志接口,它由两根线组成,数据线MDIO和时钟线MDC。SMI支持访问32个PHY,这在设备需要多个网口时非常有用,不过一般设备都只使用一个PHY。PHY芯片内部一般都有32个16位的寄存器,用于配置PHY芯片属性、工作环境、状态指示等等,当然很多PHY芯片并没有使用到所有寄存器位。MAC内核就是通过SMI向PHY的寄存器写入数据或从PHY寄存器读取PHY状态,一次只能对一个PHY的其中一个寄存器进行访问。SMI最大通信频率为2.5MHz,通过控制以太网MAC MII地址寄存器?(ETH_MACMIIAR)的CR位可选择时钟频率。 SMI is an internal MAC nuclear access PHY memory interface xff0c; it consists of two lines xff0c; data lines DIO and clockline xff0c. SMI supports access to 32 PHY, this is very useful when the equipment needs multiple portals xff0c; however, the general equipment uses only one PHY. The PHY chip usually has 32 16-bit senders xff0c; it is used to configure PHY chip properties, working environment, state instructions, etc. xff0c; of course, many PHY chips are not used to all depositors. The MAC core is used to write data through SMI's sender to PHY or from PHY's depository. SMI是通过数据帧方式与PHY通信的,帧格式如表?391,数据位传输顺序从左到右。 SMI communicates with PHY via data frames xff0c; frame formats such as tables? 391xff0c; data biting order from left to right. 表?391 SMI帧格式 Table: 391 SMI frame format 管理帧字段 Manage Frame Fields 报头(32bit) Header (32bit) 起始 Start 操作 Operation PADDR RADDR TA 数据(16bit) Data (16bit) 空闲 Free 读取 Read 111…111 01 10 ppppp rrrrr Z0 ddd…ddd Z 写入 Write 111…111 01 01 ppppp rrrrr 10 ddd…ddd Z PADDR用于指定PHY地址,每个PHY都有一个地址,一般由PHY硬件设计决定,所以是固定不变的。RADDR用于指定PHY寄存器地址。TA为状态转换域,若为读操作,MAC输出两个位高阻态,而PHY芯片则在第一位时输出高阻态,第二位时输出"0"。若为写操作,MAC输出"10",PHY芯片则输出高阻态。数据段有16位,对应PHY寄存器每个位,先发送或接收到的位对应以太网?MAC MII?数据寄存器(ETH_MACMIIDR)寄存器的位15。 PADDR is used to specify PHY address & #xff0c; each PHY has an address & #xff0c; usually PHY hardware design & #xff0c; so it is fixed. RADDR is used to specify PHY register address. TA is the status conversion field & #xff0c; #xff0c is used for reading operations & #xff0c; MAC exports two high-level barriers & xff0c; PHY chips are exported at the first time & #xff0c; 34; 0 #34; if you write operations xff0c; MAC output #34; 34 #34; #xff0c; xy chips export high barriers. Data segment has 16 xff0c; for PHY transmitters xff0c; for PHY transmitters xff0c; for sending pre-recet and #MACDID. 当以太网MAC MII地址寄存器?(ETH_MACMIIAR)的写入位和繁忙位被置1时,SMI将向指定的PHY芯片指定寄存器写入ETH_MACMIIDR中的数据。写操作时序见图?396。 When the writing and busy slot of the ETH_MACMIIAR address is 1 & #xff0c; SMI writes the data in the ETH_MACMIIDR to the specified PHY chip. 图?396 SMI写操作 Figure? 396 SMI writing. 当以太网MAC MII地址寄存器?(ETH_MACMIIAR)的写入位为0并且繁忙位被置1时,SMI将从向指定的PHY芯片指定寄存器读取数据到ETH_MACMIIDR内。读操作时序见图?397。 When the ETH_MACMIIAR (ETH_MACMIIAR) is written at 0 and busy position 1 & #xff0c; SMI will read the data from the specified PHY chip to the ETH_MACMIIDR. The reading sequence is shown in figure 397. 图?397 SMI读操作 Figure: 397 SMI read operations 介质独立接口(MII)用于理解MAC控制器和PHY芯片,提供数据传输路径。RMII接口是MII接口的简化版本,MII需要16根通信线,RMII只需7根通信,在功能上是相同的。图?398为MII接口连接示意图,图?399为RMII接口连接示意图。 The media independent interface (MII) is used to understand the MAC controller and PHY chip & #xff0c; provides a data transfer path. The RMII interface is a simplified version of the MII interface & #xff0c; MII requires 16 lines of communication & #xff0c; RMII requires only 7 lines of communication & #xff0c; it is functionally the same. 图?398 MII接口连接 Figure: 398 MII interface connection 图?399 RMII接口连接 Figure? 399 RMII interface connection ?TX_CLK:数据发送时钟线。标称速率为10Mbit/s时为2.5MHz;速率为100Mbit/s时为25MHz。RMII接口没有该线。 ?TX_CLK: Data sent the clock. The nominal speed is 2.5 MHz; at 10Mbit/s; the rate is 25 MHz at 100Mbit/s. The RRMII interface does not have this line. ?RX_CLK:数据接收时钟线。标称速率为10Mbit/s时为2.5MHz;速率为100Mbit/s时为25MHz。RMII接口没有该线。 RX_CLK: Data reception clock. The nominal speed rate is 2.5 MHz; at 10Mbit/s; the rate is 25 MHz at 100Mbit/s. The RRMII interface does not have this line. ?TX_EN:数据发送使能。在整个数据发送过程保存有效电平。 _TX_EN: Data sent enabler. Saves effective flats throughout the data sent process. ?TXD[3:0]或TXD[1:0]:数据发送数据线。对于MII有4位,RMII只有2位。只有在TX_EN处于有效电平数据线才有效。 ?TXD[3:0] or TXD[1:0] & #xff1a; data transmission lines. For MII there are 4 & #xff0c; RMII only 2. Effective only if TX_EN is in a valid level data line. ?CRS:载波侦听信号,由PHY芯片负责驱动,当发送或接收介质处于非空闲状态时使能该信号。在全双工模式该信号线无效。 ?CRS: carrier listener signal & #xff0c; PHY chip driver & #xff0c; enables the signal when sending or receiving the medium in a non-empty state. The signal line is invalid in full-time work mode. ?COL:冲突检测信号,由PHY芯片负责驱动,检测到介质上存在冲突后该线被使能,并且保持至冲突解除。在全双工模式该信号线无效。 ♪ COL: conflict detection signal xff0c; PHY chip driver xff0c; post-conflict detection of medium presence xff0c; and maintenance until the conflict is defused. The signal line is invalid in full-time mode. ?RXD[3:0]或RXD[1:0]:数据接收数据线,由PHY芯片负责驱动。对于MII有4位,RMII只有2位。在MII模式,当RX_DV禁止、RX_ER使能时,特定的RXD[3:0]值用于传输来自PHY的特定信息。 ?RXD[3:0] or RXD[1:0]: data receipt data lines & #xff0c; driven by PHY chip. For MII there are 4 & #xff0c; RMII only 2 bits. In MII mode & #xff0c; when RX_DV is disabled, RX_ER & #xff0c; specific RXD value [3:0] is used to transmit specific information from PHY. ?RX_DV:接收数据有效信号,功能类似TX_EN,只不过用于数据接收,由PHY芯片负责驱动。对于RMII接口,是把CRS和RX_DV整合成CRS_DV信号线,当介质处于不同状态时会自切换该信号状态。 ?RX_DV: Receiving data valid signal xff0c; functions similar to TX_EN, only for data reception xff0c; driven by PHY chip. For RMII interface xff0c; integrating CRS and RX_DV into CRS_DV signal xff0c; switching the signal state from one medium to another when it is in a different state. ?RX_ER:接收错误信号线,由PHY驱动,向MAC控制器报告在帧某处检测到错误。 ?RX_ER: Received error signal & #xff0c; PHY-driven xff0c; reported error detected somewhere in the frame to the MAC controller. ?REF_CLK:仅用于RMII接口,由外部时钟源提供50MHz参考时钟。 ?RF_CLK: only for RMII interface & #xff0c; 50 MHz reference clocks from external clock sources. 因为要达到100Mbit/s传输速度,MII和RMII数据线数量不同,使用MII和RMII在时钟线的设计是完全不同的。对于MII接口,一般是外部为PHY提供25MHz时钟源,再由PHY提供TX_CLK和RX_CLK时钟。对于RMII接口,一般需要外部直接提供50MHz时钟源,同时接入MAC和PHY。 For MII interfaces & #xff0c; generally external provision of 25 MHz clocks to PHYs & #xff0c; then PHY provides TX_CLK and RX_CLK clocks. For RMII interfaces & #xff0c; usually external direct provision of 50 MHz clocks #xff0c; and access to MAC and PHY. 开发板板载的PHY芯片型号为LAN8720A,该芯片只支持RMII接口,电路设计时参考图?399。 The PHY chip type on the development plate is LAN8720A, the chip only supports the RMII interface & #xff0c; the circuit reference diagram?399. ETH相关硬件在STM32F42x控制器分布参考表?392。 ETH-related hardware in STM32F42x controller distribution reference table? 392. 表?392 ETH复用引脚 Table? 392 ETH repeat kicks. ETH(AF11) GPIO MII MII_TX_CLK PC3 MII_TXD0 PB12/PG13 MII_TXD1 PB13/PG14 MII_TXD2 PC2 MII_TXD3 PB8/PE2 MII_TX_EN PB11/PG11 MII_RX_CLK PA1 MII_RXD0 PC4 MII_RXD1 PC5 MII_RXD2 PB0/PH6 MII_RXD3 PB1/PH7 MII_RX_ER PB10/PI10 MII_RX_DV PA7 MII_CRS PA0/PH2 MII_COL PA3/PH3 RMII RMII_TXD0 PB12/PG13 RMII_TXD1 PB13/PG14 RMII_TX_EN PG11 RMII_RXD0 PC4 RMII_RXD1 PC5 RMII_CRS_DV PA7 RMII_REF_CLK PA1 SMI MDIO PA2 MDC PC1 其他 Other PPS_OUT PB5/PG8 其中,PPS_OUT是IEEE 1588定义的一个时钟同步机制。 Of which xff0c; PPS_OUT is a clock synchronization mechanism as defined by IEEE 1588. ETH外设负责MAC数据包发送和接收。利用DMA从系统寄存器得到数据包数据内容,ETH外设自动填充完成MAC数据包封装,然后通过PHY发送出去。在检测到有MAC数据包需要接收时,ETH外设控制数据接收,并解封MAC数据包得到解封后数据通过DMA传输到系统寄存器内。 ETH external is responsible for sending and receiving the MAC data package. DMA is used to obtain data content from the system repository xff0c; ETH external is used to complete the MAC data package wrapping xff0c; then it is sent out via PHY. When xff0c is detected that a MAC data package needs to be received xff0c; ETH external control data reception xff0c; and unsealed MAC data packages are transferred to the system repository via DMA. MAC数据帧发送全部由DMA控制,从系统存储器读取的以太网帧由DMA推入FIFO,然后将帧弹出并传输到MAC内核。帧传输结束后,从MAC内核获取发送状态并传回DMA。在检测到SOF(Start Of Frame)时,MAC接收数据并开始MII发送。在EOF(End Of Frame)传输到MAC内核后,内核将完成正常的发送,然后将发送状态返回给DMA。如果在发送过程中发送常规冲突,MAC内核将使发送状态有效,然后接受并丢弃所有后续数据,直至收到下一SOF。检测到来自MAC的重试请求时,应从SOF重新发送同一帧。如果发送期间未连续提供数据,MAC将发出下溢状态。在帧的正常传输期间,如果MAC在未获得前一帧的EOF的情况下接收到SOF,则将忽略该SOF并将新的帧视为前一帧的延续。 MAC data frames are sent all by DMA control & #xff0c; an Ether frame read from the system memory is pushed into FIFO, then the frame is ejected and transferred to the MAC kernel. After frame transfer xff0c; after delivery xff0c; from MAC kernel to DMA. When sent to SOF (Start Of Frame) xff0c; MAC kernels will send data effectively xff0c; MACs will receive and drop all follow-up data after transmission to the MAC xff0c; until the next SCF is detected x0c; #Fffffs will be sent without continuous transmission #xOx0; SffSpints will be sent without Ox0; FfSpint #0Spint Ox0S. MAC控制MAC数据包的发送操作,它会自动生成前导字段和SFD以及发送帧状态返回给DMA,在半双工模式下自动生成阻塞信号,控制jabber(MAC看门狗)定时器用于在传输字节超过2048字节时切断数据包发送。在半双工模式下,MAC使用延迟机制进行流量控制,程序通过将ETH_MACFCR寄存器的BPA位置1来请求流量控制。MAC包含符合IEEE 1588的时间戳快照逻辑。MAC数据包发送时序参考图?3910。 MAC controls the sending of the MAC data package xff0c; it automatically generates the lead field and SFID and the sending frame back to DMA, automatically generates the blocking signal xff0c in semi-double working mode; controls the Jabber (MAC door dog) timer used to sever the delivery of the data package when the transmission byte exceeds 2048 bytes. Under semi-duration mode xff0c; MAC uses a delay mechanism to conduct flow control xff0c; requests traffic control by placing the ETH_MACFCR repository at BPA position 1. MAC contains a time stamp logic consistent with IEE 1588. MAC data packages send time series reference maps?3910. 图?3910 MAC数据包发送时序(无冲突) Figure? 3910 MAC data pack dispatch time series (no conflict) MAC接收到的数据包填充RX FIFO,达到FIFO设定阈值后请求DMA传输。在默认直通模式下,当FIFO接收到64个字节(使用ETH_DMAOMR寄存器中的RTC位配置)或完整的数据包时,数据将弹出,其可用性将通知给DMA。DMA向AHB接口发起传输后,数据传输将从FIFO持续进行,直到传输完整个数据包。完成EOF帧的传输后,状态字将弹出并发送到DMA控制器。在Rx FIFO存储转发模式(通过ETH_DMAOMR寄存器中的RSF位配置)下,仅在帧完全写入Rx FIFO后才可读出帧。 MAC received data packages filled with RX FIFO, requests for DMA transfer after reaching the FIFO set threshold. xff0c under default direct mode; xff0c when FIFO receives 64 bytes (using the RTC bit configuration in the ETH_DMAOMR register) or complete data packages xff0c; the data will eject xff0c; its availability will be notified to DMA. xff0c after DMA initiates transmission to the AHB interface; xff0c from FIFO on a continuous basis until the transfer of the full data package is completed. The status word will eject and send to the DMA controller. 当MAC在MII上检测到SFD时,将启动接收操作。MAC内核将去除报头和SFD,然后再继续处理帧。检查报头字段以进行过滤,FCS字段用于验证帧的CRC如果帧未通过地址滤波器,则在内核中丢弃该帧。MAC数据包接收时序参考图?3911。 When MAC detects SFD on MII & #xff0c; the reception operation will be activated. The MAC kernel will remove the header and SFD& #xff0c; then continue processing the frame. Check the header field for filtering & #xff0c; the FCS field will be used by the CRC to verify the frame if the frame does not pass through the address filter & #xff0c; discards the frame in the kernel. The MAC data package is received with a reference chart?3911. 图?3911 MAC数据包接收时序(无错误) Figure? 3911 MAC data package acceptance time series (no error) MAC过滤功能可以选择性的过滤设定目标地址或源地址的MAC帧。它将检查所有接收到的数据帧的目标地址和源地址,根据过滤选择设定情况,检测后报告过滤状态。针对目标地址过滤可以有三种,分别是单播、多播和广播目标地址过滤;针对源地址过滤就只有单播源地址过滤。 The MAC filters can be selective in setting the MAC frames of the target address or source address. It will check the target and source addresses of all data frames received & #xff0c; xff0c based on filter selection; and post-detection reporting filter status. There are three xff0cs for target addresses; xff1b for single, multiple and broadcast target addresses; and only single source addresses for source locations are filtered. 单播目标地址过滤是将接收的相应DA字段与预设的以太网MAC地址寄存器内容比较,最高可预设4个过滤MAC地址。多播目标地址过滤是根据帧过滤寄存器中的HM位执行对多播地址的过滤,是对MAC地址寄存器进行比较来实现的。单播和多播目标地址过滤都还支持Hash过滤模式。广播目标地址过滤通过将帧过滤寄存器的BFD位置1使能,这使得MAC丢弃所有广播帧。 The single target address filter is a comparison of the recipient's corresponding DA field with the predefined Ethernet MAC address register xff0c; a maximum of four predefined filter MAC addresses. The multiple target address filter is implemented on the basis of HM in the frame filter register xff0c; it is a comparison of the MAC address register. The single and multicast target address filter also supports the Hash filter mode. The broadcast target address filter enables xff0c by filtering the BFD position 1 of the frame carrier; this causes MAC to discard all broadcast frames. 单播源地址过滤是将接收的SA字段与SA寄存器内容进行比较过滤。 The single-source address filter is a comparison of the SA fields received with the contents of the SA register. MAC过滤还具备反向过滤操作功能,即让过滤结构求补集。 MAC filters also have reverse filtering operations & #xff0c; i.e. allow filter structures to supplement them. LAN8720A是SMSC公司(已被Microchip公司收购)设计的一个体积小、功耗低、全能型10/100Mbps的以太网物理层收发器。它是针对消费类电子和企业应用而设计的。LAN8720A总共只有24Pin,仅支持RMII接口。由它组成的网络结构见图?3912。 LAN8720A is a small, low-capacity, full-power 10/100Mbps transceiver designed by SMSC (which has been acquired by Microchip). It is designed for consumer electronics and business applications. LAN8720A totals only 24 Pin, supports only the RRMII interface. Its network structure is shown in figure 3912. 图?3912?由LAN8720A组成的网络系统结构 Figure 3912: Structure of the network system consisting of LAN8720A LAN8720A通过RMII与MAC连接。RJ45是网络插座,在与LAN8720A连接之间还需要一个变压器,所以一般使用带电压转换和LED指示灯的HY911105A型号的插座。一般来说,必须为使用RMII接口的PHY提供50MHz的时钟源输入到REF_CLK引脚,不过LAN8720A内部集成PLL,可以将25MHz的时钟源陪频到50MHz并在指定引脚输出该时钟,所以我们可以直接使其与REF_CLK连接达到提供50MHz时钟效果。 LAN8720A connects to MAC via RMII. RJ45 is a network plug & #xff0c; a transformer & #xff0c is also needed between links to LAN8720A; therefore, the HY91105A model is generally used for electrical voltage conversion and LED light. & #xff0c in general; it is necessary to provide 50 MHz clock source input to RF_CLK and #xff0c using RMII interfaces; but LAN8720A is internally integrated into PLL, 25MHz clocks are available to 50 MHz and the clock #xff0c is exported at the point of destination; so we can directly link it to RF_CLK to provide 50 MHz clock effect. LAN8720A内部系统结构见图?3913。 The structure of the LAN8720A internal system is shown in figure 3913. 图?3913 LAN8720A内部系统结构 Figure: 3913 LAN8720A internal system structure LAN8720A有各个不同功能模块组成,最重要的要数接收控制器和发送控制器,其它的基本上都是与外部引脚挂钩,实现信号传输。部分引脚是具有双重功能的,比如PHYAD0与RXER引脚是共用的,在系统上电后LAN8720A会马上读取这部分共用引脚的电平,以确定系统的状态并保存在相关寄存器内,之后则自动转入作为另一功能引脚。 LAN8720A has various functional modules comprising xff0c; the most important number receiver controller and send controller xff0c; the others are basically linked to external pullers xff0c; achieve signal transmission. Part of the induction is a dual function xff0c; for example, the PHYAD0 and RXER foot are shared xff0c; once the system is electrolyzed, LAN8720A will read this share xff0c; determine the state of the system and save it in the relevant transmitter xff0c; and then automatically transfer it to another feature. PHYAD[0]引脚用于配置SMI通信的LAN8720A地址,在芯片内部该引脚已经自带下拉电阻,默认认为0(即使外部悬空不接),在系统上电时会检测该引脚获取得到LAN8720A的地址为0或者1,并保存在特殊模式寄存器(R18)的PHYAD位中,该寄存器的PHYAD有5个位,在需要超过2个LAN8720A时可以通过软件设置不同SMI通信地址。PHYAD[0]是与RXER引脚共用。 PHYAD [0] quotes are used to configure SMI communications at the LAN8720A address & #xff0c; the lead foot has been pulled off from within the chip & #xff0c; the default is 0 (even if the external space is not open) & #xff0c; the lead foot is detected for receiving LAN8720A at an address of 0 or 1xff0c while on the system; and it is stored in the PHYAD slot of the special mode sender (R18) xff0c; the sender has 5 places xff0c; a different SMI address can be set up by software if more than two LAN8720As are required. PHYAD [0] is shared with RXER quotes. MODE[2:0]引脚用于选择LAN8720A网络通信速率和工作模式,可选10Mbps或100Mbps通信速度,半双工或全双工工作模式,另外LAN8720A支持HP Auto-MDIX自动翻转功能,即可自动识别直连或交叉网线并自适应。一般将MODE引脚都设置为1,可以让LAN8720A启动自适应功能,它会自动寻找最优工作方式。MODE[0]与RXD0引脚共用、MODE[1]与RXD1引脚共用、MODE[2]与CRS_DV引脚共用。 MODE[2:0] is used to select LAN8720A network communication speed and mode of operation & #xff0c; 10 Mbps or 100 Mbps communication speed & #xff0c; half- or full-time mode of work & #xff0c; and LAN8720A supports HP Auto-Return function & #xff0c; it automatically recognizes and adapts to direct or cross-network links. The MODE index is generally set to 1xff0c; it allows LAN8720A to start self-adaptation & #xff0c; it automatically seeks the best working methods. MODE[0] shares with RXD0 guides, MODE[1] shares with RXD1 guides, MODE[2] shares with CRRS_DV guides. nINT/REFCLKO引脚用于RMII接口中REF_CLK信号线,当nINTSEL引脚为低电平是,它也可以被设置成50MHz时钟输出,这样可以直接与STM32F42x的REF_CLK引脚连接为其提供50MHz时钟源,这种模式要求为XTAL1与XTAL2之间或为XTAL1/CLKIN提供25MHz时钟,由LAN8720A内部PLL电路陪频得到50MHz时钟,此时nIN/REFCLKO引脚的中断功能不可用,用于50MHz时钟输出。当nINTSEL引脚为高电平时,LAN8720A被设置为时钟输入,即外部时钟源直接提供50MHz时钟接入STM32F42x的REF_CLK引脚和LAN8720A的XTAL1/CLKIN引脚,此时nINT/REFCLKO可用于中断功能。nINTSEL与LED2引脚共用,一般使用下拉 NINT/REFCLKO is used for the RF_CLK signal line & #xff0c in the RMII interface; it can also be set up as a 50 MHz clock output xff0c; it can be provided with 50 MHz clocks CLKs link directly to STM32F42x & xff0cs; this mode requires 25 MHz clocks between XTAL1 and XTAL2 or XTALKIN xff0cs; it can be provided with 50 MHz clocks xff0cs from the LAN8720A internal PL circuits; when the NN/REFCLKs are not available for interruption of the Xff0cs; it can be used for the CKKKLs & TKLs TKs Ls Ls Ls ; it can be used as an external source of LXLFs ; it can be used for the TKHLs =50 hours SILLLs T & T & Ls L L L ; it is used as an external source of Ls L L T L. REGOFF引脚用于配置内部+1.2V电压源,LAN8720A内部需要+1.2V电压,可以通过VDDCR引脚输入+1.2V电压提供,也可以直接利用LAN8720A内部+1.2V稳压器提供。当REGOFF引脚为低电平时选择内部+1.2V稳压器。REGOFF与LED1引脚共用。 REGOFF is used to configure internal & #43; 1.2V voltage & #xff0c; LAN8720A internal needs & #43; 1.2V voltage & #xff0c; can enter 43; 1.2V voltage & #xff0c via VDDDR; also direct use of LAN8720A internal & #43; 1.2V stabilizer. Select internal & #43; 1.2V stabilizer when REGOFF is low level. RGOFF is shared with LED1. SMI支持寻址32个寄存器,LAN8720A只用到其中14个,参考表?393。 SMI supported the location of 32 senders & #xff0c; LAN8720A used only 14 of them & #xff0c; reference table? 393. 表?393 LAN8720A寄存器列表 Table? 393 LAN8720A register list 序号 Serial number 寄存器名称 Cannot initialise Evolution's mail component. 分组 Group 0 Basic Control Register Basic 1 Basic Status Register Basic 2 PHY Identifier 1 Extended 3 PHY Identifier 2 Extended 4 Auto-Negotiation Advertisement Register Extended 5 Auto-Negotiation Link Partner Ability Register Extended 6 Auto-Negotiation Expansion Register Extended 17 Mode Control/Status Register Vendor-specific 18 Special Modes Vendor-specific 26 Symbol Error Counter Register Vendor-specific 27 Control / Status Indication Register Vendor-specific 29 Interrupt Source Register Vendor-specific 30 Interrupt Mask Register Vendor-specific 31 PHY Special Control/Status Register Vendor-specific 序号与SMI数据帧中的RADDR是对应的,这在编写驱动时非常重要,本文将它们标记为R0~R31。寄存器可规划为三个组:Basic、Extended和Vendor-specific。Basic是IEEE 802.3要求的,R0是基本控制寄存器,其位15为Soft Reset位,向该位写1启动LAN8720A软件复位,还包括速度、自适应、低功耗等等功能设置。R1是基本状态寄存器。Extended是扩展寄存器,包括LAN8720A的ID号、制造商、版本号等等信息。Vendor-specific是供应商自定义寄存器,R31是特殊控制/状态寄存器,指示速度类型和自适应功能。 The serial number and RADDR in the SMI data frame correspond to xff0c; this is very important at the time of writing the drive xff0c; they are marked as R0~R31. The transmitter can be planned for three groups xff1a; Basic, Extendeded and Vendor-specific. Basic is xff0c; R0 is the basic control repository xff0c; it is the basic control depositor xff0c; it is the 15 Soft Reet bit xff0c; it is the start-up of LAN8720A software xff0c to that location 1; it also includes the functions of speed, self-adaptation, low power consumption etc. R1 is the basic status depositor xff0c; Extended is the extension register xff0c; it includes information on the LAN8720A ID, manufacturer, version, etc. LwIP是Light Weight Internet Protocol?的缩写,是由瑞士计算机科学院Adam Dunkels等开发的适用于嵌入式领域的开源轻量级TCP/IP协议栈。它可以移植到含有操作系统的平台中,也可以在无操作系统的平台下运行。由于它开源、占用的RAM和ROM比较少、支持较为完整的TCP/IP协议、且十分便于裁剪、调试,被广泛应用在中低端的32位控制器平台。可以访问网站:http://savannah.nongnu.org/projects/lwip/?获取更多LwIP信息。 LwIP is a Light Weight Internet Protocol? & #xff0c; an open-source light TCP/IP platform for embedded areas, developed by the Swiss Academy of Computer Sciences Adam Dunkels and others. It can be transplanted to a platform containing an operating system & #xff0c; it can also run under a platform with no operating system. It has a relatively small number of RAMs and RPMs, supports a more complete TCP/IP and is very easy to tailor, calibrate xff0c; it is widely applied to a 32-bit control platform at the lower and middle end. It can access the website xff1a; http://savannah.nongnu.org/projects/lwip/? for more LwIP information. 目前,LwIP最新更新到1.4.1版本,我们在上述网站可找到相应的LwIP源码下载通道。我们下载两个压缩包:lwip-1.4.1.zip和contrib-1.4.1.zip,lwip-1.4.1.zip包括了LwIP的实现代码,contrib-1.4.1.zip包含了不同平台移植LwIP的驱动代码和使用LwIP实现的一些应用实例测试。 Currently xff0c; LwIP update to version 1.4.1 xff0c; we can find the corresponding LwIP source downloads on the above-mentioned website. We download two compressed packages xff1a; lwip-1.4.1.zip and contrib-1.4.1.zip, lwip-1.4.1.zip includes the LwIP implementation code xff0c; contrib-1.4.1.zip contains the driver code of different platforms to transplant LwIP and some practical tests of applications performed using LwIP. 但是,遗憾的是contrib-1.4.1.zip并没有为STM32平台提供实例,这对于初学者想要移植LwIP来说难度还是非常大的。ST公司也是认识到LwIP在嵌入式领域的重要性,所以他们针对LwIP应用开发了测试平台,其中有一个是在STM32F4x7系列控制器运行的(文件编号为:STSW-STM32070),虽然我们的开发板平台是STM32F429控制器,但经测试发现关于ETH驱动部分以及LwIP接口函数部分是可以通用的。为减少移植工作量,我们选择使用ST官方例程相关文件,特别是ETH底层驱动部分函数,这样我们也可以花更多精力在理解代码实现方法上。 However, xff0c; unfortunately, contrib-1.4.1.zip did not provide an example of STM32 platform xff0c; this is still very difficult for beginners to attempt to transplant LwIP. ST also recognizes the importance of LwIP in embedded fields xff0c; so it developed a testing platform for LwIP applications xff0c; one of these was run by STM32F4x7 controllers (document number xff1a; STSW-STM3270) xfff0c; although our development board platform is STM32F429 controller xff0c; it was tested that the ETH drivers and the LwIP interface functions were common. To reduce the transplant workload xff0c; we chose to use the SST official routine related document xff0c; in particular, the #fff0c drive function at the bottom of ETH #xff0c; so we could also devote more effort to understanding the method of achieving the code.39.3.2?各网络层的功能

39.4 以太网外设(ETH)

39.4.1?SMI接口

1.SMI帧格式

2.SMI读写操作

39.4.2?MII和RMII接口

39.4.3?MAC数据包发送和接收

1.MAC数据包发送

2.MAC数据包接收

39.4.4?MAC过滤

39.5 PHY:LAN8720A

39.6 LwIP:轻型TCP/IP协议栈

注册有任何问题请添加 微信:MVIP619 拉你进入群

打开微信扫一扫

添加客服

进入交流群

发表评论